#

# Synthesis and Characterizations of Ternary InGaAs Nanowires by a Two-Step Growth Method for High-Performance Electronic Devices

Jared J. Hou,<sup>†</sup> Ning Han,<sup>†</sup> Fengyun Wang,<sup>‡</sup> Fei Xiu,<sup>†</sup> SenPo Yip,<sup>†</sup> Alvin T. Hui,<sup>†</sup> TakFu Hung,<sup>†</sup> and Johnny C. Ho<sup>†,\*</sup>

<sup>†</sup>Department of Physics and Materials Science and <sup>‡</sup>Department of Biology and Chemistry, City University of Hong Kong, Tat Chee Avenue, Kowloon, Hong Kong SAR, China

n recent years, due to the low electron mass and corresponding high carrier mobility, indium arsenide (InAs) nanowires (NWs) has been extensively studied for high-speed and high-frequency electronic devices.<sup>1–8</sup> Meanwhile, because of the large Bohr radius, the InAs NW is also one of the excellent candidates to study quantum confinement effects.9 However, further applications still suffer from the significant leakage current in InAs NW-based devices arising mainly from its small electronic band gap (0.34 eV). Although there has been significant progress in tackling this problem by altering the atomic structures, such as InAs/InP heterojunction<sup>10</sup> and InAsP segment along the InAs NWs,<sup>11</sup> a new NW materials system that does not rely on complicated heterostructures to solve the problem is still lacking.

Among many alternative materials, the ternary indium gallium arsenide (InGaAs) system is demonstrated as a promising thin-film channel material which has a relatively larger band gap to alleviate the leakage current issue and at the same time not sacrifice the high electron mobility;12-14 nevertheless, there are few reports on the synthesis and characterization of this In-GaAs NW material. Studies of terahertz emission<sup>15</sup> and photovoltaic<sup>16</sup> applications of InGaAs NWs have been recently demonstrated, but there is still very limited studies on the detailed fundamental electrical transport properties of InGaAs NWs. Importantly, those NWs are highly defective with significant twin defects and inversion domains,<sup>15,17</sup> which are expected to scatter carriers to degrade their electrical performance.<sup>18–20</sup> In this paper, we present a simple technique to synthesize highly crystalline InGaAs NWs by a novel two-step chemical vapor deposition

### ABSTRACT

InAs nanowires have been extensively studied for high-speed and high-frequency electronics due to the low effective electron mass and corresponding high carrier mobility. However, further applications still suffer from the significant leakage current in InAs nanowire devices arising from the small electronic band gap. Here, we demonstrate the successful synthesis of ternary InGaAs nanowires in order to tackle this leakage issue utilizing the larger band gap material but at the same time not sacrificing the high electron mobility. In this work, we adapt a two-step growth method on amorphous SiO<sub>2</sub>/Si substrates which significantly reduces the kinked morphology and surface coating along the nanowires. The grown nanowires exhibit excellent crystallinity and uniform stoichiometric composition along the entire length of the nanowires. More importantly, the electrical properties of those nanowires are found to be remarkably impressive with  $I_{ON}/I_{OFF}$  ratio >10<sup>5</sup>, field-effect mobility of ~2700 cm<sup>2</sup>/(V·s), and ON current density of ~0.9 mA/ $\mu$ cm. These nanowires are then employed in the contact printing and achieve large-scale assembly of nanowire parallel arrays which further illustrate the potential for utilizing these high-performance nanowires on substrates for the fabrication of future integrated circuits.

**KEYWORDS:** indium gallium arsenide nanowires · two-step growth method · solid-source chemical vapor deposition · high-performance electronics · nanowire contact printing

(CVD) method with a high growth yield. From experimental results, the NWs exhibit impressive electrical performance with a  $I_{ON}/I_{OFF}$ ratio of ~10<sup>5</sup> and field-effect mobility of ~2700 cm<sup>2</sup>/(V·s) when configured in the back-gate NW field-effect transistors (FETs). Utilizing the NW printing approach,<sup>21,22</sup> highperformance InGaAs NW parallel array devices \* Address correspondence to johnnyho@cityu.edu.hk.

Received for review March 4, 2012 and accepted March 25, 2012.

Published online March 26, 2012 10.1021/nn300966j

HOU ET AL.

VOL. 6 • NO. 4 • 3624–3630 • 2012 American Chemical Society

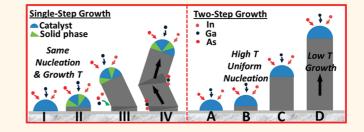

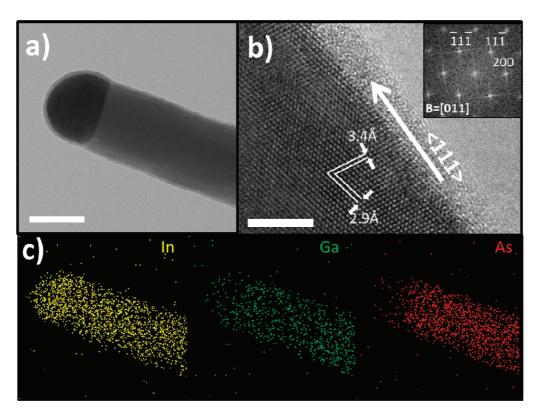

Figure 1. Single-step growth method. (a) Schematic of growth mechanism of the single-step method, demonstrating the kinked morphology and surface coating form gradually during the NW growth. (b) SEM and (inset) TEM images of NWs grown by the single-step method (growth condition: source temperature at 820 °C, substrate temperature at 520 °C, H<sub>2</sub> flow rate at 400 sccm, and growth duration for 30 min). The scale bars are 500 nm for SEM and 200 nm for TEM. (c) Growth process window summary of the single-step growth method, holding source temperature constant at 820 °C. Solid symbol designates the high NW growth density (>5 NW/ $\mu$ m<sup>2</sup>), while open symbol indicates the low NW density (~1 NW/ $\mu$ m<sup>2</sup>).

are fabricated, which further illustrates the technological potential of InGaAs NWs for next-generation electronic devices.

### **RESULTS AND DISCUSSION**

InGaAs NWs used in this study were synthesized using a catalytic solid-source CVD method similar to the ones previously reported.<sup>23,24</sup> Here, only the In-rich InGaAs NWs would be the focus to ensure the opening of the band gap without degrading the excellent carrier mobility as compared to the ones of InAs NWs. Since the vapor pressure of Ga is higher than that of In atoms,<sup>25,26</sup> an equal weight of InAs and GaAs powders was mixed and utilized in this In-rich NW growth. In brief, during the growth, Au nanoparticles were used as catalysts and obtained by thermal annealing (~800 °C for 10 min) of a predeposited 0.5 nm thick evaporated Au layer on 50 nm thick SiO<sub>2</sub>/Si substrates. Then the subsequent growth temperatures, both source and substrate zones, as well as flow rate of carrier gas, H<sub>2</sub>, were carefully adjusted to control the physical properties of NWs. Notably, a two-step growth technique was adopted which has been utilized in other NW materials systems.<sup>27,28</sup> Compared to the conventional singlestep CVD that contains only one regular growth step, the two-step approach has an additional nucleation step at a higher temperature before the regular growth step. Regarding our InGaAs NW system, this method

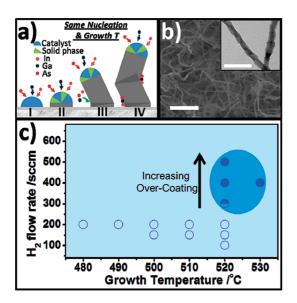

Figure 2. Two-step growth method. (a) Schematic of the growth mechanism of the two-step method. (b) SEM and (inset) TEM images of NWs grown by the two-step method (growth condition: source temperature at 800 °C, substrate temperature at 540 °C, H<sub>2</sub> flow rate at 100 sccm, growth duration of first step is 1 min and second step is 30 min); the scale bars are 2  $\mu$ m and 200 nm, respectively. (c) Growth window summary of two-step method, holding H<sub>2</sub> flow rate at 100 sccm. Compared to single-step method, NWs produced by this two-step method have a much broader growth window, which provides the higher process parameter tolerance in the NW growth. Solid symbol designates the high NW growth density (>5 NW/ $\mu$ m<sup>2</sup>), while open symbol indicates the low NW density (~1 NW/ $\mu$ m<sup>2</sup>).

could significantly reduce the kinked morphology, defect density, as well as surface coating around NWs compared to a single-step method.

Specifically, as shown in Figure 1a, in the single-step growth, Au catalysts were first formed on the substrate during the annealing stage. Afterward, the temperature was cooled to the growth temperature and the precursor vapors were started to supply from the source zone (stage I). However, at this moment, the catalyst nanoparticles may not be homogeneous in the liquid or solid phase because of similar temperatures between the catalytic eutectoids and the NW growth;<sup>29</sup> in this case, rather, some solid phase may coexist with the liquid phase within the catalysts (stage II), which is commonly observed in the synthesis of Asbased NWs.<sup>27,29</sup> This physical phase inversion within the catalysts could hinder the growth rate of NWs at the catalyst-NW interface and lead to the unevenly distributed growth rate, which is the main reason of kinked morphology (stage III). Meanwhile, during the growth process, the precursor source atoms may impinge and diffuse onto the kinked surface due to the heterogeneous catalytic favorable sites.<sup>30</sup> When the growth time prolongs, all of these would eventually induce a severe overcoating problem (stage IV). As depicted in Figure 1b, InGaAs NWs grown by this single-step method have indeed serious kinked morphology. On the basis of the transmission electron

VOL.6 • NO.4 • 3624-3630 • 2012

agnanc www.acsnano.org microscope (TEM) image (Figure 1b inset and see Supporting Information Figure S1), irregular surface coating exists along the entire length of the NWs. When the growth pressure or gas flow increases, the amount of coating gets more severe due to the shorter mean free path of precursor vapors. Importantly, after summarizing the results of more than 50 growth trails, the process window of this single-step approach is found to be guite narrow, as illustrated in Figure 1c; only growth temperatures of 520–530 °C and H<sub>2</sub> gas flow higher than 300 sccm (source temperature constant at 820 °C) can produce NWs with a decent density  $(>5 \text{ NW}/\mu\text{m}^2)$ . Any other conditions deviated from this window would not result in any NW growth or gives NWs with a very low growth yield (<1 NW/ $\mu$ m<sup>2</sup>). This tight window would be mainly attributed to the inhomogeneous catalytic phase which makes the NW nucleation process difficult and sensitive to the growth temperature and pressure.

In contrast, as demonstrated in Figure 2b and its inset, InGaAs NWs grown by the two-step method exhibit much more straightness as well as smoother surface (no overcoating). These obvious differences could be explained by the difference in growth mechanisms between these two techniques. In the two-step growth approach, the first nucleation step is performed at a higher temperature (~600 °C), significantly reducing the chances of solid phase formation within the catalysts (stages A and B). Therefore, NWs will grow more uniformly at the catalyst-NW interface and nurture along a certain growth direction without the kinked structures formed; this way, the source vapor atoms would not easily deposit onto the NW surface directly to form the surface coating, and they will be more likely to migrate into the catalyst region following the standard vapor-liquid-solid (VLS) growth process (stages C and D). The two-step grown InGaAs NWs are typically found to have a length exceeding 10  $\mu$ m and an average diameter of 30 nm uniformly along the length of the NWs. In this case, this two-step method is expected to be less sensitive to the growth condition. As shown in Figure 2c, summarizing more than 100 growth trials, there is indeed a much wider growth process window spanning the source and growth temperatures between 720-800 and 520-560 °C, respectively, and a low gas flow of H<sub>2</sub> (~100 sccm) is purposely utilized to minimize the formation of overcoating. Notably, this broad experimental parameter tolerance will certainly offer a great processing flexibility for the synthesis of InGaAs and other III-V NWs.

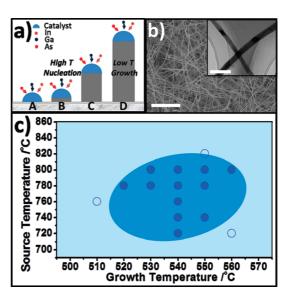

In order to further characterize the NWs grown by this two-step technique, high-resolution TEM (HRTEM) is utilized to study the structural properties of these NWs. As depicted in Figure 3a, a spherical catalytic seed is observed at the tip of a typical NW, which confirms the VLS growth mechanism. The corresponding selected area electron diffraction (SAED) pattern further illustrates its singlecrystalline zinc blende (ZB) structure and its preferential growth orientation in the  $\langle 111 \rangle$  direction (see Supporting Information Figure S2). This growth direction is dominant in other observed NWs, which corresponds well to several studies in III-V nanowire synthesis where the  $\langle 111 \rangle$  direction is the major one because of the lowest surface energy in  $\{111\}$  planes.<sup>31,32</sup> Although there are a few dark bands in the low-resolution TEM image (Figure 2b), which are believed to be stacking faults, however, the majority of the NWs are uniform and in the low defect concentration, as demonstrated in the HRTEM image in Figure 3b. Also, the spacings between the adjacent lattice planes are found to be 0.34 and 0.29 nm, which are in good agreement with the plane spacing of {111} and {200} equivalent planes in the Inrich thin-film counterparts, respectively.<sup>33</sup> The thickness of the native oxide amorphous layer is about 2.5 nm, which is consistent with other reported III-V 1D nanostructures.<sup>2,25</sup> Notably, no wurtzite structure is observed under SAED or HRTEM characterization. All of these indicate the good crystallinity of NWs grown by this two-step technique.

Moreover, one of the challenges in synthesizing high-performance III-V nanowires is to control the NW stoichiometry uniformly and precisely to enable various devices fabrications. For ternary NWs such as InGaAs, this stoichiometric problem appears to be even more challenging because the chemically increased degree of freedom may easily induce atomic aggregation and clusters in the NW body, degrading the electrical properties of NWs.<sup>18-20</sup> In this case, as shown in Figure 3c, the energy-dispersive X-ray spectrometric (EDS) elemental mapping of same NW (Figure 3a,b) demonstrates the homogeneous distribution of In, Ga, and As atoms along the NW body. To further shed light to quantify the corresponding chemical composition, EDS line scan is performed along the NW axial direction across from the tip to body (see Supporting Information Figures S3 and S4). On the basis of the line scan, the catalyst mainly contains In and Au atoms while the Au content drops drastically once passing the catalyst-NW interface. This observation suggests that no significant Au diffusion occurs in NW body which may damage the crystallinity and electrical properties, and the approximate AuIn composition in the catalyst agrees well with the previous report on Au-catalyzed InAs NWs.<sup>34</sup> Also, no As concentration is found in the tip, indicating that the solubility of As in Au eutectoids is low<sup>35</sup> and As atoms would react in the tip/NW interface to induce the NW growth.<sup>34–36</sup> On the other hand, little Ga content exists in the catalyst, which could be attributed to the faster diffusion of Ga compared to In atoms and also the purposely Ga deficient precursor vapors; therefore, Ga atoms are continuously consumed in the growth interface for the formation of In-rich NWs. In addition, more than 10 NWs are studied by the EDS analysis in detail, and they all exhibit the NW composition of  $\ln_x Ga_{1-x}$ As with x ranging from 0.65 to 0.73. All of these have demonstrated the remarkably

VOL.6 • NO.4 • 3624-3630 • 2012

Figure 3. Typical single-crystalline NW with the uniform stoichiometry. (a) STEM image of a representative InGaAs NW. (b) HRTEM of the corresponding NW. The scale bar is 5 nm. (Inset) Fast Fourier transform (FFT) image of the NW body, showing a ZB structure with the  $\langle 111 \rangle$  growth direction; (c) EDS elemental mapping of the NW in panel a. The representative NW has uniform In-rich composition across the NW body.

good control of the NW stoichiometry with this simple two-step technique. Notably, it would be fundamentally interesting to vary the NW composition to Ga-rich regions and study their corresponding physical properties; however, a recent study of  $In_{0.5}Ga_{0.5}As$  and other Ga-rich NWs showed the high defect density<sup>15</sup> probably deteriorating the carrier transport along the NW,<sup>18–20</sup> while more investigation is currently in process.

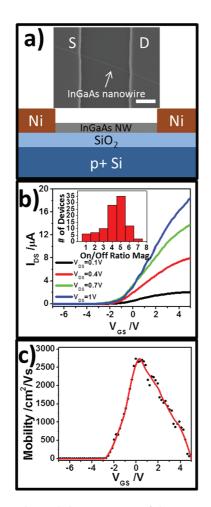

To shed light studying the electrical properties of InGaAs NWs, as shown in Figure 4a, field-effect transistors (FETs) were fabricated by using Ni ( $\sim$ 50 nm) source/drain (S/D) metal contacts in a common backgated configuration (50 nm thermal oxide as the gate dielectric and heavily B-doped Si substrate as the gate). The electrical performance of a representative FET consisting of an individual InGaAs NW as the channel material with the diameter of  $d \sim 21$  nm (NW diameter  $\sim$  26 nm with  $\sim$ 5 nm native oxide shell) and a channel length of L  $\sim$  2.64  $\mu$ m is shown in Figure 4b. The NW FET exhibits n-type conduction as expected, and under  $V_{\rm DS} = 1$  V, it achieves 19  $\mu$ A ON current under  $V_{\rm GS} = 5$  V and a 100 pA OFF current under  $V_{GS} = -7$  V. This ON current corresponds to a current density of  $\sim$ 0.9 mA/ $\mu$ m as normalized with the NW diameter (effective channel width), which is comparable to that of the state-of-theart Si MOSFETs ( $\sim$ 1 mA/ $\mu$ m). Although this ON current is similar to the InAs NW FET,<sup>3</sup> consequently, it gives a much better  $I_{ON}/I_{OFF}$  ratio (~10<sup>5</sup>; see Supporting

Information Figure S5). In contrast to another previous study of InGaAs NWs grown by MOVPE, the same  $I_{ON}/I_{OFE}$ ratio can only be obtained for the measurement performed at 1.5 K.<sup>37</sup> Also, the ON–OFF ratio statistics (Figure 4b inset) further demonstrate this typically high ratio  $(>10^4)$ being dominant across all of the devices, as  $\sim$ 80% of 100 measured devices fall into this category. Furthermore, the corresponding field-effect mobility is calculated in Figure 4c as a function of back-gate voltage  $V_{GS}$ . Specifically, the transconductance  $(g_m = (dl_{DS})/(dV_{GS})|V_{DS})$ at low bias  $V_{\rm DS}$  = 0.1 V is assessed, and the mobility is deduced by standard square law model  $\mu = q_{\rm m}(L^2/L^2)$  $C_{\rm ox}$ )(1/ $V_{\rm DS}$ ), where  $C_{\rm ox}$  is the gate capacitance obtained from the finite element analysis software COMSOL with respect to the different diameter of the nanowire. The calculated peak mobility is about  $\sim$ 2700 cm<sup>2</sup>/(V·s), which is comparable to the state-of-the-art InAs NW FET.<sup>2</sup> All of these have indicated the excellent crystal quality of NWs achieved in this simple two-step technique.

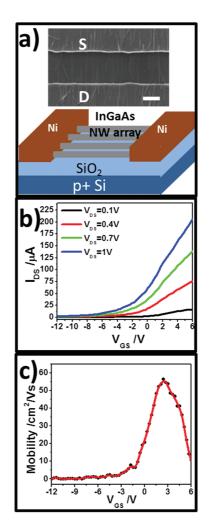

In order to further demonstrate the feasibility of large-scale integration of the NWs for electronic applications, the well-established NW contact printing method<sup>1,23,24</sup> is utilized to fabricate InGaAs NW parallel arrays following the same device fabrication. Figure 5a shows the SEM image and schematic of the printed NW array FET, while Figure 5b demonstrates the electrical transport of a printed array with ~200 nanowires in the channel (width ~200  $\mu$ m and length ~2  $\mu$ m).

VOL.6 • NO.4 • 3624-3630 • 2012

A

www.acsnano.org

Figure 4. Electrical characterization of the representative single NW FET. (a) (Top) SEM image and (bottom) schematic of a back-gated InGaAs nanowire FET with Ni S/D metal contacts; the scale bar is 1  $\mu$ m. (b) Transfer characteristic of a back-gated InGaAs NW FET with  $d \sim 21$  nm and  $L \sim 2.6 \,\mu$ m for  $V_{\rm DS} = 0.1$ , 0.4, 0.7, and 1 V. The inset shows the statistics of  $I_{\rm ON}/I_{\rm OFF}$  ratio sampling from 100 InGaAs NW FET devices obtained from the same NW growth trial. (c) Mobility assessment under  $V_{\rm DS} = 0.1$  V of the device in panel b. The black dotted line is the experiment data, and the solid red line is the fitted data curve.

This device delivers a current density of 1  $\mu$ A/ $\mu$ m under  $V_{\rm DS}$  = 1 V and  $V_{\rm GS}$  = 6 V, with an  $I_{\rm ON}/I_{\rm OFF}$  ratio of  $\sim$ 500 (see Support Information Figure S6). As shown in Figure 5c, the corresponding field-effect mobility against gate voltage  $V_{GS}$  is also evaluated, and the mobility is calculated based on the standard square law model similar to the operation of the single NW device. The capacitance is estimated using an upper-bound model that multiplies the capacitance from every single nanowire and the number of nanowires in the channel.<sup>38</sup> The calculated peak mobility is found to be  $\sim$ 60 cm<sup>2</sup>/(V · s) and on the same level of the state-of-theart semiconductor carbon nanotube networks.<sup>39</sup> Compared to the single NW device (Figure 4), the average current level of each NW gets degraded, which could be attributed to different NW-to-NW gate coupling due to the misalignment and broken wires in the channel

Figure 5. Electrical characterization of the representative InGaAs NW parallel array FET. (a) (Top) SEM and (bottom) schematic of a back-gated InGaAs NW array FET. The scale bar is 1  $\mu$ m. The designated channel length and width are 2 and 200  $\mu$ m, respectively. (b) Transfer characteristic of a representative InGaAs NW parallel device under  $V_{DS} = 0.1, 0.4, 0.7,$  and 1 V, about 200 NWs bridging S/D. (c) Mobility assessment of this NW array device under  $V_{DS} = 0.1$  V. The black dotted line is the experimental data, and the solid red line is the fitted data curve.

leading to the parasitic capacitance, both of which will significantly increase the total capacitance and decrease current output. Further enhancement of the mobility can be achieved in the future by the passivation of the NW surfaces such as the  $(NH_4)_2S$  treatment,<sup>40–42</sup> while current investigations are ongoing. In the future, the NW device performance can also be further improved through the enhancement of NW print density, alignment, channel length scaling, and the integration of high-*k* dielectric in the top-gated structures.

## CONCLUSION

In conclusion, a two-step growth method in the solid-source chemical vapor deposition to synthesize ternary InGaAs nanowires is presented. This approach could significantly reduce the kinked morphology and issue of surface coating problem. The grown InGaAs

VOL.6 • NO.4 • 3624-3630 • 2012

3628

nanowires have remarkable single crystallinity as well as uniformly distributed stoichiometric composition of In, Ga, and As based on this simple growth technique. By fabricating back-gate field-effect transistors, the impressive ON current densities (~0.9 mA/ $\mu$ m,  $I_{ON}/I_{OFF}$ ratio (>10<sup>5</sup>), and electron mobility (~2700 cm<sup>2</sup>/(V·s)) are obtained, demonstrating the success of lowering the leakage current without sacrificing the carrier mobility as compared to the state-of-the-art InAs nanowire devices. These InGaAs nanowires are then employed in the contact printing and generate largescale assembly of nanowire parallel arrays that could be utilized in the fabrication of future high-performance integrated circuits.

### **METHODS**

Nanowire Synthesis. InGaAs nanowires were synthesized on an amorphous SiO<sub>2</sub>/Si wafer in a two-zone furnace using a chemical vapor transport method. InAs and GaAs powders were mixed in a designated ratio (50 wt % InAs/50 wt % GaAs) and loaded into a boron nitride crucible in the upstream of the furnace. The growth substrate, deposited with 0.5 nm Au film in thermal evaporator, was positioned in the downstream. H<sub>2</sub> (99.9995%) was used as carrier gas to transport the evaporated source materials to the growth substrate. The temperature in the downstream was first elevated to 800 °C and remained at that temperature for 10 min in order to anneal the Au catalyst. For the single-step growth method, the temperature was then cooled directly to the growth temperature (~15 min after annealing stop). Then the upstream started to heat, and when the source temperature reached the designated value, the growth began. For the two-step growth method, the substrate temperature was first cooled to the nucleation temperature  $(\sim 10 \text{ min after annealing})$  when the source temperature started to elevate. When the source temperature reached the designated value, the nucleation step began. After 1-2 min, the downstream stopped heating and started to cool again to a second step growth temperature (approximately 6-8 min after heating stop). During the growth, the flow rate of H<sub>2</sub> was maintained at 100 sccm and the corresponding pressure downstream is  ${\sim}$ 1 Torr. The grown nanowires were taken out of the furnace after the system was cooled naturally to room temperature.

Single NW Device Fabrication and Characterization. After CVD growth, the InGaAs nanowires were first harvested by sonication in high-purity ethanol solution. Then we randomly drop-cast the nanowires onto precleaned highly doped p-type Si substrates, with a 50 nm thermal grown gate oxide. These substrates, 1.5 cm  $\times$  1.5 cm in size, were then spin-coated with LOR and AZ5206 photoresist and were exposed to ultraviolet light and went through developing. After we get the source and drain pattern, a 50 nm thick Ni will be thermally deposited as the contact electrodes followed by a lift-off process. Electrical performance of fabricated back-gated FETs was characterized with a standard electrical probe station and Agilent 4155C semiconductor analyzer.

**Printing Device Fabrication and Characterization.** NW arrays were printed on doped p-type SiO<sub>2</sub>/Si substrates, and these substrate were then spin-coated with LOR and AZ5206 photoresist and went through lithography and developing, followed by Ni electrode deposition and lift-off. Before electrical characterization, the NW arrays were then soaked in (NH<sub>4</sub>)<sub>2</sub>S solution in order to passivate the surface of the NWs. After passivation, the devices were rinsed carefully using DI water and ethanol and baked at 120 °C for 60 min. Electrical performance of fabricated NW arrays FETs was then characterized with a standard electrical probe station and Agilent 4155C semiconductor analyzer.

*Conflict of Interest:* The authors declare no competing financial interest.

Acknowledgment. This research was supported by the General Research Fund of the Research Grants Council of Hong Kong SAR, China, under Project Nos. CityU 101210 and CityU 101111.

Supporting Information Available: TEM images of the kinked NW with surface coating; SAED of a typical InGaAs NW; the

corresponding EDS line scan on the NW; EDS spectrum within the NW body; electrical I–V measurements of the single NW FET and parallel nanowire array FET, respectively. This material is available free of charge *via* the Internet at http://pubs.acs.org.

### **REFERENCES AND NOTES**

- Takahashi, T.; Takei, K.; Adabi, E.; Fan, Z. Y.; Niknejad, A. M.; Javey, A. Parallel Array InAs Nanowire Transistors for Mechanically Bendable, Ultrahigh Frequency Electronics. ACS Nano 2010, 4, 5855–5860.

- Ford, A. C.; Ho, J. C.; Chueh, Y. L.; Tseng, Y. C.; Fan, Z. Y.; Guo, J.; Bokor, J.; Javey, A. Diameter-Dependent Electron Mobility of InAs Nanowires. *Nano Lett.* **2009**, *9*, 360–365.

- Ford, A.; Ho, J.; Fan, Z.; Ergen, O.; Altoe, V.; Aloni, S.; Razavi, H.; Javey, A. Synthesis, Contact Printing, and Device Characterization of Ni-Catalyzed, Crystalline InAs Nanowires. *Nano Res.* 2008, 1, 32–39.

- Egard, M.; Johansson, S.; Johansson, A. C.; Persson, K. M.; Dey, A. W.; Borg, B. M.; Thelander, C.; Wernersson, L. E.; Lind, E. Vertical InAs Nanowire Wrap Gate Transistors with f<sub>t</sub> > 7 GHz and f<sub>Max</sub> > 20 GHz. *Nano Lett.* **2010**, *10*, 809–812.

- Ham, D.; Nam, S.; Jiang, X. C.; Xiong, Q. H.; Lieber, C. M. Vertically Integrated, Three-Dimensional Nanowire Complementary Metal-Oxide-Semiconductor Circuits. *Proc. Natl. Acad. Sci. U.S.A.* 2009, *106*, 21035–21038.

- Thelander, C.; Froberg, L. E.; Rehnstedt, C.; Samuelson, L.; Wemersson, L. E. Vertical Enhancement-Mode InAs Nanowire Field-Effect Transistor with 50-nm Wrap Gate. *IEEE Electron Device Lett.* **2008**, *29*, 206–208.

- Dayeh, S. A.; Aplin, D. P. R.; Zhou, X. T.; Yu, P. K. L.; Yu, E. T.; Wang, D. L. High Electron Mobility InAs Nanowire Field-Effect Transistors. *Small* **2007**, *3*, 326–332.

- Thelander, C.; Bjork, M. T.; Larsson, M. W.; Hansen, A. E.; Wallenberg, L. R.; Samuelson, L. Electron Transport in InAs Nanowires and Heterostructure Nanowire Devices. *Solid State Commun.* 2004, *131*, 573–579.

- Zanolli, Z.; Pistol, M. E.; Froberg, L. E.; Samuelson, L. Quantum-Confinement Effects in InAs–InP Core–Shell Nanowires. J. Phys.: Condens. Matter 2007, 19, 295219.

- Jiang, X. C.; Xiong, Q. H.; Nam, S.; Qian, F.; Li, Y.; Lieber, C. M. InAs/InP Radial Nanowire Heterostructures as High Electron Mobility Devices. *Nano Lett.* 2007, 7, 3214–3218.

- Lind, E.; Persson, A. I.; Samuelson, L.; Wernersson, L. E. Improved Subthreshold Slope in an InAs Nanowire Heterostructure Field-Effect Transistor. *Nano Lett.* 2006, *6*, 1842–1846.

- Xuan, Y.; Wu, Y. Q.; Ye, P. D. High-Performance Inversion-Type Enhancement-Mode InGaAs MOSFET with Maximum Drain Current Exceeding 1 A/mm. *IEEE Electron Device Lett.* 2008, 29, 294–296.

- Xuan, Y.; Wu, Y. Q.; Lin, H. C.; Shen, T.; Ye, P. D. Submicrometer Inversion-Type Enhancement-Mode InGaAs MOSFET with Atomic-Layer-Deposited Al<sub>2</sub>O<sub>3</sub> as Gate Dielectric. *IEEE Electron Device Lett.* **2007**, *28*, 935–938.

- Goel, N.; Majhi, P.; Chui, C. O.; Tsai, W.; Choi, D.; Harris, J. S. InGaAs Metal-Oxide-Semiconductor Capacitors with HfO<sub>2</sub> Gate Dielectric Grown by Atomic-Layer Deposition. *Appl. Phys. Lett.* **2006**, *89*, 163517.

- Jung, C. S.; Kim, H. S.; Jung, G. B.; Gong, K. J.; Cho, Y. J.; Jang, S. Y.; Kim, C. H.; Lee, C. W.; Park, J. Composition and Phase

Tuned InGaAs Alloy Nanowires. J. Phys. Chem. C **2011**, *115*, 7843–7850.

- Shin, J. C.; Kim, K. H.; Yu, K. J.; Hu, H.; Yin, L.; Ning, C.-Z.; Rogers, J. A.; Zuo, J.-M.; Li, X. In<sub>x</sub>Ga<sub>1-x</sub>As Nanowires on Silicon: One-Dimensional Heterogeneous Epitaxy, Bandgap Engineering, and Photovoltaics. *Nano Lett.* **2011**, *11*, 4831–4838.

- Heiss, M.; Ketterer, B.; Uccelli, E.; Ramon Morante, J.; Arbiol, J.; Fontcuberta i Morral, A. In(Ga)As Quantum Dot Formation on Group-III Assisted Catalyst-Free InGaAs Nanowires. *Nanotechnology* **2011**, *22*, 195601.

- Ikejiri, K.; Kitauchi, Y.; Tomioka, K.; Motohisa, J.; Fukui, T. Zinc Blende and Wurtzite Crystal Phase Mixing and Transition in Indium Phosphide Nanowires. *Nano Lett.* **2011**, *11*, 4314–4318.

- Wallentin, J.; Ek, M.; Wallenberg, L. R.; Samuelson, L.; Borgström, M. T. Electron Trapping in InP Nanowire FETs with Stacking Faults. *Nano Lett.* **2011**, *12*, 151–155.

- Schroer, M. D.; Petta, J. R. Correlating the Nanostructure and Electronic Properties of InAs Nanowires. *Nano Lett.* 2010, 10, 1618–1622.

- Fan, Z. Y.; Ho, J. C.; Jacobson, Z. A.; Yerushalmi, R.; Alley, R. L.; Razavi, H.; Javey, A. Wafer-Scale Assembly of Highly Ordered Semiconductor Nanowire Arrays by Contact Printing. *Nano Lett.* **2008**, *8*, 20–25.

- Takahashi, T.; Nichols, P.; Takei, K.; Ford, A. C.; Jamshidi, A. Wu, M. C.; Ning, C. Z.; Javey, A. Contact Printing of Compositionally Graded CdS<sub>x</sub>Se<sub>1-x</sub> Nanowire Parallel Arrays for Tunable Photodetectors. *Nanotechnology* **2012**, *23*, 045201.

- Han, N.; Wang, F. Y.; Hui, A. T.; Hou, J. J.; Shan, G. C.; Xiu, F.; Hung, T. F.; Ho, J. C. Facile Synthesis and Growth Mechanism of Ni-Catalyzed GaAs Nanowires on Non-crystalline Substrates. *Nanotechnology* **2011**, *22*, 285607.

- Han, N.; Hui, A. T.; Wang, F. Y.; Hou, J. J.; Xiu, F.; Hung, T. F.; Ho, J. C. Crystal Phase and Growth Orientation Dependence of GaAs Nanowires on Ni<sub>x</sub>Ga<sub>y</sub> Seeds via Vapor– Solid–Solid Mechanism. *Appl. Phys. Lett.* **2011**, *99*, 083114.

- 25. Goldstein, B.; Szostak, D. J.; Ban, V. S. Langmuir Evaporation from the (100), (111A), and (111B) Faces of GaAs. *Surf. Sci.* **1976**, *57*, 733–740.

- Bimberg, D.; Ledentsov, N. N.; Grundmann, M.; Kirstaedter, N.; Schmidt, O. G.; Mao, M. H.; Ustinov, V. M.; Egorov, A. Y.; Zhukov, A. E.; Kopev, P. S.; *et al.* InAs–GaAs Quantum Pyramid Lasers: *In Situ* Growth, Radiative Lifetimes and Polarization Properties. *Jpn. J. Appl. Phys.* **1996**, *35*, 1311– 1319.

- Joyce, H. J.; Gao, Q.; Tan, H. H.; Jagadish, C.; Kim, Y.; Zhang, X.; Guo, Y.; Zou, J. Twin-Free Uniform Epitaxial GaAs Nanowires Grown by a Two-Temperature Process. *Nano Lett.* 2007, 7, 921–926.

- Greytak, A. B.; Lauhon, L. J.; Gudiksen, M. S.; Lieber, C. M. Growth and Transport Properties of Complementary Germanium Nanowire Field-Effect Transistors. *Appl. Phys. Lett.* 2004, 84, 4176.

- Piccin, M.; Bais, G.; Grillo, V.; Jabeen, F.; De Franceschi, S.; Carlino, E.; Lazzarino, M.; Romanato, F.; Businaro, L.; Rubini, S.; *et al.* Growth by Molecular Beam Epitaxy and Electrical Characterization of GaAs Nanowires. *Phys. E* 2007, *37*, 134–137.

- Wacaser, B. A.; Dick, K. A.; Johansson, J.; Borgström, M. T.; Deppert, K.; Samuelson, L. Preferential Interface Nucleation: An Expansion of the VLS Growth Mechanism for Nanowires. *Adv. Mater.* **2009**, *21*, 153–165.

- Fortuna, S. A.; Wen, J.; Chun, I. S.; Li, X. Planar GaAs Nanowires on GaAs (100) Substrates: Self-Aligned, Nearly Twin-Defect Free, and Transfer-Printable. *Nano Lett.* 2008, 8, 4421–4427.

- Ihn, S.-G.; Song, J.-I.; Kim, T.-W.; Leem, D.-S.; Lee, T.; Lee, S.-G.; Koh, E. K.; Song, K. Morphology- and Orientation-Controlled Gallium Arsenide Nanowires on Silicon Substrates. *Nano Lett.* **2007**, *7*, 39–44.

- Kim, T. W. Strain Effects and Crystal Structures of the In<sub>x</sub>Ga<sub>1-x</sub>as Active Layer in the Highly Lattice-Mismatched In<sub>x</sub>Ga<sub>1-x</sub>As/InP Modulation-Doped Coupled Double Quantum Wells. *Solid State Commun.* **1999**, *110*, 69–73.

- Dick, K. A.; Deppert, K.; Karlsson, L. S.; Wallenberg, L. R.; Samuelson, L.; Seifert, W. A New Understanding of Au-Assisted Growth of III–V Semiconductor Nanowires. *Adv. Funct. Mater.* 2005, *15*, 1603–1610.

- Dick, K. A.; Deppert, K.; Mårtensson, T.; Mandl, B.; Samuelson, L.; Seifert, W. Failure of the Vapor–Liquid–Solid Mechanism in Au-Assisted MOVPE Growth of InAs Nanowires. *Nano Lett.* 2005, *5*, 761–764.

- Tchernycheva, M.; Travers, L.; Patriarche, G.; Glas, F.; Harmand, J.-C.; Cirlin, G. E.; Dubrovskii, V. G. Au-Assisted Molecular Beam Epitaxy of InAs Nanowires: Growth and Theoretical Analysis. *J. Appl. Phys.* 2007, *102*, 094313–094318.

- Noborisaka, J.; Sato, T.; Motohisa, J.; Hara, S.; Tomioka, K.; Fukui, T. Electrical Characterizations of InGaAs Nanowire-Top-Gate Field-Effect Transistors by Selective-Area Metal Organic Vapor Phase Epitaxy. *Jpn. J. Appl. Phys.* 2007, 46, 7562–7568.

- Fan, Z. Y.; Ho, J. C.; Takahashi, T.; Yerushalmi, R.; Takei, K.; Ford, A. C.; Chueh, Y. L.; Javey, A. Toward the Development of Printable Nanowire Electronics and Sensors. *Adv. Mater.* 2009, *21*, 3730–3743.

- Wang, C.; Chien, J.-C.; Takei, K.; Takahashi, T.; Nah, J.; Niknejad, A. M.; Javey, A. Extremely Bendable, High-Performance Integrated Circuits Using Semiconducting Carbon Nanotube Networks for Digital, Analog, and Radio-Frequency Applications. *Nano Lett.* **2012**, *12*, 1527– 1533.

- van Tilburg, J. W. W.; Algra, R. E.; Immink, W. G. G.; Verheijen, M.; Bakkers, E. P. A. M.; Kouwenhoven, L. P. Surface Passivated InAs/InP Core/Shell Nanowires. *Semicond. Sci. Technol.* **2010**, *25*, 024011.

- Gong, X. Y.; Yamaguchi, T.; Kan, H.; Makino, T.; Ohshimo, K.; Aoyama, M.; Kumagawa, M.; Rowell, N. L.; Rinfret, R. Sulphur Passivation of InAs(Sb). *Appl. Surf. Sci.* **1997**, *113*, 388–392.

- Eassa, N.; Murape, D. M.; Neethling, J. H.; Betz, R.; Coetsee, E.; Swart, H. C.; Venter, A.; Botha, J. R. Chalcogen Based Treatment of InAs with (NH<sub>4</sub>)<sub>2</sub>S/(NH<sub>4</sub>)<sub>2</sub>SO<sub>4</sub>. Surf. Sci. 2011, 605, 994–999.